# Design with Hardware Description Languages (HDL)

(DHDL-94952)

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

mehranzadeh@iaud.ac.ir Mehran.students@gmail.com

## **Code Structure**

Amin Mehranzadeh, Ph.D.

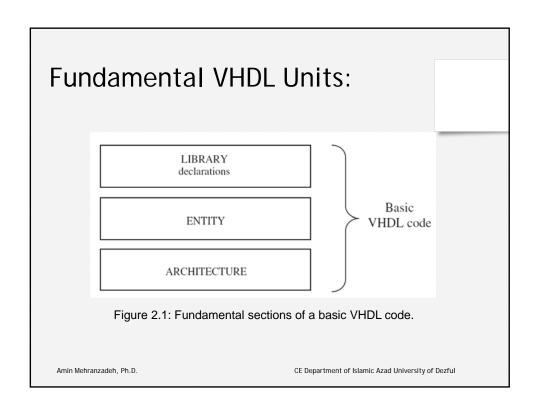

#### **Fundamental VHDL Units:**

- a standalone piece of VHDL code is composed of at least three fundamental sections:

- -LIBRARY declarations:

Contains a list of all libraries to be used in the design. For example: ieee, std, work, etc.

- ENTITY: Specifies the I/O pins of the circuit.

- ARCHITECTURE: Contains the VHDL code proper, which describes how the circuit should behave (function).

Amin Mehranzadeh, Ph.D.

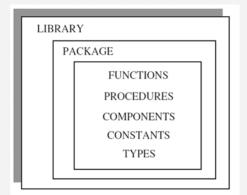

#### LIBRARY:

- A LIBRARY is a collection of commonly used pieces of code. Placing such pieces inside a library allows them to be reused or shared by other designs.

- The typical structure of a library is usually written in the form of FUNCTIONS, PROCEDURES, or COMPONENTS, which are placed inside PACKAGES, and then compiled into the destination library.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### LIBRARY:

Figure 2.2 :Fundamental parts of a LIBRARY.

Amin Mehranzadeh, Ph.D.

## **Library Declarations:**

To declare a LIBRARY (that is, to make it visible to the design) two lines of code are needed, one containing the name of the library, and the other a use clause, as shown in the syntax below.

LIBRARY library\_name;

USE library\_name.package\_name.package\_parts;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **Library Declarations:**

• At least three packages, from three different libraries, are usually needed in a design:

ieee.std\_logic\_1164 (from the ieee library), standard (from the std library), and work (work library).

Amin Mehranzadeh, Ph.D.

### **Library Declarations:**

Their declarations are as follows:

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- the end of a statement or

LIBRARY std;

-- declaration, while a double

USE std.standard.all;

LIBRARY work;

USE work.all;

```

The libraries std and work shown above are made visible by default, so there is no need to declare them; only the ieee library must be explicitly written. However, the latter is only necessary when the STD\_LOGIC (or STD\_ULOGIC) data type is employed in the design.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **Library Declarations:**

- The std\_logic\_1164 package of the ieee library specifies a multi-level logic system.

- std is a resource library (data types, text i/o, etc.) for the VHDL design environment.

- work library is where we save our design (the .vhd file, plus all files created by the compiler, simulator, etc.).

Amin Mehranzadeh, Ph.D.

| F | N | Т | -1 | T | Υ | • |

|---|---|---|----|---|---|---|

|   | N |   |    |   |   | _ |

An ENTITY is a list with specifications of all input and output pins (PORTS) of the circuit. Its syntax is shown below.

```

ENTITY entity_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END entity_name;

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **ENTITY:**

An ENTITY is a list with specifications of all input and output pins (PORTS) of the circuit. Its syntax is shown below.

```

ENTITY entity_name IS

PORT (

port_name : signal_mode signal_type;

port_name : signal_mode signal_type;

...);

END entity_name;

```

Amin Mehranzadeh, Ph.D.

#### **ENTITY:**

The mode of the <u>signal</u> can be IN, OUT, INOUT, or BUFFER. IN and OUT are truly unidirectional pins, while INOUT is bidirectional. BUFFER is employed when the output signal must be used (read) internally.

IN →

Circuit 4

→ INOUT

→ BUFFER

The type of the signal can be BIT, STD\_LOGIC, INTEGER, etc.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **ENTITY:**

• Example: Let us consider the NAND gate. Its ENTITY can be specified as:

Note: the name of the entity can be basically any name, except VHDL reserved words.

Amin Mehranzadeh, Ph.D.

#### **ARCHITECTURE:**

• The ARCHITECTURE is a description of how the circuit should behave (function). Its syntax is the following:

```

ARCHITECTURE architecture_name OF entity_name IS

[declarations]

BEGIN

(code)

END architecture_name;

```

As shown above, an architecture has two parts: a declarative part (optional), where signals and constants (among others) are declared, and the code part (from BEGIN down).

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **ARCHITECTURE:**

• Example: Let us consider the NAND gate.

```

ARCHITECTURE myarch OF nand_gate IS

BEGIN

x <= a NAND b;

END myarch;

```

In this example, there is no declarative part, and the code contains just a single assignment.

Amin Mehranzadeh, Ph.D.

#### **Examples:**

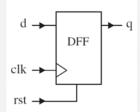

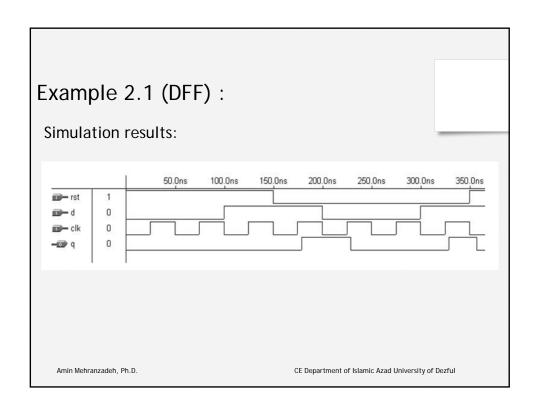

• Example 2.1: DFF with Asynchronous Reset.

Figure shows the diagram of a D-type flip-flop (DFF), triggered at the <u>risingedge of the clock</u> signal (clk), and with an <u>asynchronous reset</u> input (rst). When rst = '1', the output must be turned low, regardless of clk. Otherwise, the output must copy the input (that is,  $q \le d$ ) at the moment when clk changes from '0' to '1' (that is, when an upward event occurs on clk).

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### Example 2.1 (DFF): 2 LIBRARY ieee: 3 USE ieee.std\_logic\_1164.all; 5 ENTITY dff IS PORT ( d, clk, rst: IN STD\_LOGIC; q: OUT STD\_LOGIC); 8 END dff; One thing to remember: 9 ----however, is that VHDL is 10 ARCHITECTURE behavior OF dff IS inherently concurrent (contrary 11 BEGIN to regular computer programs, 12 PROCESS (rst, clk) which are sequential), so to implement any clocked circuit 14 IF (rst='1') THEN using a PROCESS. 19 END PROCESS; 20 END behavior: Amin Mehranzadeh, Ph.D. CE Department of Islamic Azad University of Dezful

```

Example 2.1 (DFF): 1 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

5 ENTITY dff IS

PORT ( d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

Note2:

8 END dff;

The "<=" operator is used to 9 -----

assign a value to a SIGNAL. In

10 ARCHITECTURE behavior OF dff IS

contrast, ":=" would be used for a VARIABLE. All ports in an 12 PRO

PROCESS (rst, clk)

BEGIN

13

entity are signals by default.

IF (rst='1') THEN

14

q <= '0';

15

16

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

18

19

END PROCESS;

20 END behavior;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

#### Example 2.2 (DFF plus NAND Gate): 2 ENTITY example IS 3 PORT ( a, b, clk: IN BIT; DFF q: OUT BIT); 5 END example; clk-6 -----7 ARCHITECTURE example OF example IS SIGNAL temp : BIT; ← Notice that there is 9 BEGIN no mode declaration 10 temp <= a NAND b;</pre> (mode is only used in 11 PROCESS (clk) entities). 12 BEGIN line 10 is executed IF (clk'EVENT AND clk='1') THEN q<=temp; 13 concurrently with 14 END IF; the block 11-15. 15 END PROCESS; 16 END example; Amin Mehranzadeh, Ph.D. CE Department of Islamic Azad University of Dezful