# Design with Hardware Description Languages (HDL)

(DHDL-94952)

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

mehranzadeh@iaud.ac.ir Mehran.students@gmail.com

# **Operators and Attributes**

Amin Mehranzadeh, Ph.D.

# Operators:

- VHDL provides several kinds of pre-defined operators:

- Assignment operators

- · Logical operators

- Arithmetic operators

- Relational operators

- Shift operators

- Concatenation operators

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# **Assignment Operators:**

- Are used to assign values to signals, variables, and constants. They are:

- <= Used to assign a value to a SIGNAL.

- := Used to assign a value to a VARIABLE, CONSTANT, or GENERIC. Used also for establishing initial values.

- => Used to assign values to individual vector elements or with OTHERS.

Amin Mehranzadeh, Ph.D.

# **Assignment Operators:**

• Example: Consider the following signal and variable declarations:

```

SIGNAL x : STD_LOGIC;

VARIABLE y : STD_LOGIC_VECTOR(3 DOWNTO 0); -- Leftmost bit is MSB

SIGNAL w: STD_LOGIC_VECTOR(0 TO 7); -- Rightmost bit is

-- MSB

Then the following assignments are legal:

x <= '1'; -- '1' is assigned to SIGNAL x using "<="

y := "0000"; -- "0000" is assigned to VARIABLE y using ":="

w <= "100000000"; -- LSB is '1', the others are '0'

w <= (0 =>'1', OTHERS =>'0'); -- LSB is '1', the others are '0'

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

# **Logical Operators:**

- Used to perform logical operations. The data must be of type BIT, STD\_LOGIC, or STD\_ULOGIC (or, obviously, their respective extensions, BIT\_VECTOR, STD\_LOGIC\_VECTOR, or STD\_ULOGIC\_VECTOR).

- The logical operators are:

NOT, AND, OR, NAND, NOR, XOR, XNOR

```

Notes: The NOT operator has precedence over the others.

```

```

Examples:

y <= NOT a AND b; -- (a'.b)

y <= NOT (a AND b); -- (a.b)'

y <= a NAND b; -- (a.b)'

```

Amin Mehranzadeh, Ph.D.

# **Arithmetic Operators:**

- Used to perform arithmetic operations. The data can be of type <u>INTEGER</u>, <u>SIGNED</u>, <u>UNSIGNED</u>, or <u>REAL</u> (recall that the last cannot be synthesized directly).

- Also, if the std\_logic\_signed or the std\_logic\_unsigned package of the ieee library is used, then <u>STD\_LOGIC\_VECTOR</u> can also be employed directly in <u>addition</u> and <u>subtraction</u> operations

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# **Arithmetic Operators:**

Arithmetic Operators:

Amin Mehranzadeh, Ph.D.

# **Arithmetic Operators:**

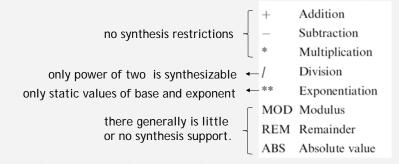

- There are no synthesis restrictions regarding addition and subtraction, and multiplication.

- For division, only power of two dividers (shift operation) are allowed.

- For exponentiation, only static values of base and exponent are accepted.

- Regard y mod x returns the remainder of y/x with the signal of x, while y rem x returns the remainder of y/x with the signal of y.

- Finally, abs returns the absolute value.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# **Comparison Operators:**

- Used for making comparisons. The data can be of any of the types listed above. The relational (comparison) operators are:

- = Equal to

- /= Not equal to

- < Less than

- > Greater than

- <= Less than or equal to

- >= Greater than or equal to

Amin Mehranzadeh, Ph.D.

# **Shift Operators:**

Used for shifting data. They were introduced in VHDL93. Their syntax is the following:

<left operand> <shift operation> <right operand>.

The left operand must be of type BIT\_VECTOR, while the right operand must be an INTEGER (+ or - in front of it is accepted). The shift operators are:

sll Shift left logic – positions on the right are filled with '0's

srl Shift right logic – positions on the left are filled with '0's

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Data Attributes:

- The pre-defined, synthesizable data attributes are the following:

- · d'LOW: Returns lower array index

- · d'HIGH: Returns upper array index

- · d'LEFT: Returns leftmost array index

- · d'RIGHT: Returns rightmost array index

- · d'LENGTH: Returns vector size

- · d'RANGE: Returns vector range

- · d'REVERSE\_RANGE: Returns vector range in reverse order

Amin Mehranzadeh, Ph.D.

### Data Attributes:

#### • Example1:

```

Example: Consider the following signal:

SIGNAL d: STD_LOGIC_VECTOR (7 DOWNTO 0);

Then:

d:LOW=0 d:HIGH=7 d:LEET=7 d:PIGHT=0 d:LENGTH=8

```

d'LOW=0, d'HIGH=7, d'LEFT=7, d'RIGHT=0, d'LENGTH=8, d'RANGE=(7 downto 0), d'REVERSE\_RANGE=(0 to 7).

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Data Attributes:

### • Example2:

```

Example: Consider the following signal:

```

```

SIGNAL x: STD_LOGIC_VECTOR (0 TO 7);

```

Then all four LOOP statements below are synthesizable and equivalent.

```

FOR i IN RANGE (0 TO 7) LOOP ...

FOR i IN x'RANGE LOOP ...

FOR i IN RANGE (x'LOW TO x'HIGH) LOOP ...

FOR i IN RANGE (0 TO x'LENGTH-1) LOOP ...

```

Amin Mehranzadeh, Ph.D.

### Data Attributes:

- If the signal is of enumerated type, then:

- · d'VAL(pos): Returns value in the position specified

- · d'POS(value): Returns position of the value specified

- · d'LEFTOF(value): Returns value in the position to the left of the value specified

- · d'VAL(row, column): Returns value in the position specified; etc.

Note: There is little or no synthesis support for enumerated data type attributes.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Data Attributes:

#### • Signal Attributes:

Let us consider a signal s. Then:

- s'EVENT: Returns true when an event occurs on s

- · s'STABLE: Returns true if no event has occurred on s

- s'ACTIVE: Returns true if s = '1'

- s'QUIET (time): Returns true if no event has occurred during the time specified

- · s'LAST\_EVENT: Returns the time elapsed since last event

- s'LAST\_ACTIVE: Returns the time elapsed since last s = '1'

- s'LAST\_VALUE: Returns the value of s before the last event; etc.

Amin Mehranzadeh, Ph.D.

### Data Attributes:

#### Signal Attributes:

Let us consider a signal s. Then:

- s'EVENT: Returns true when an event occurs on s

- s'STABLE: Returns true if no event has occurred on s

- s'ACTIVE: Returns true if s = '1'

- s'QUIET (time): Returns true if no event has occurred during the time specified

- s'LAST\_EVENT: Returns the time elapsed since last event

- s'LAST\_ACTIVE: Returns the time elapsed since last s = '1'

- s'LAST VALUE: Returns the value of s before the last event; etc.

Note: Though most signal attributes are for simulation purposes only, the first two in the list above are synthesizable, s'EVENT being the most often used of them all.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Data Attributes:

• Example: All four assignments shown below are synthesizable and equivalent. They return TRUE when an event (a change) occurs on clk, AND if such event is upward (in other words, when a rising edge occurs on clk).

```

IF (clk'EVENT AND clk='1')... -- EVENT attribute used

-- with IF

IF (NOT clk'STABLE AND clk='1')... -- STABLE attribute used

-- with IF

WAIT UNTIL (clk'EVENT AND clk='1'); -- EVENT attribute used

-- with WAIT

IF RISING_EDGE(clk)... -- call to a function

```

Amin Mehranzadeh, Ph.D.

### **User-Defined Attributes:**

VHDL also allows the construction of user defined attributes. To employ a user-defined attribute, it must be declared and specified. The syntax is the following:

Attribute declaration:

ATTRIBUTE attribute\_name: attribute\_type;

#### Attribute specification:

ATTRIBUTE attribute\_name OF target\_name: class IS value;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

### **User-Defined Attributes:**

- where:

- attribute\_type:any data type (BIT, INTEGER, STD\_LOGIC\_VECTOR, etc.)

- class: TYPE, SIGNAL, FUNCTION, etc.

- value: '0', 27, "00 11 10 01", etc.

Note: A user-defined attribute can be declared anywhere, except in a PACKAGE BODY. When not recognized by the synthesis tool, it is simply ignored, or a warning is issued.

Amin Mehranzadeh, Ph.D.

### **User-Defined Attributes:**

- where:

- attribute\_type:

any data type (BIT, INTEGER, STD\_LOGIC\_VECTOR, etc.)

- class: TYPE, SIGNAL, FUNCTION, etc.

- value: '0', 27, "00 11 10 01", etc.

#### Example:

```

ATTRIBUTE number_of_inputs: INTEGER; -- declaration

ATTRIBUTE number_of_inputs OF nand3: SIGNAL IS 3; -- specification

...

inputs <= nand3'number_of_pins; -- attribute call, returns 3

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

### **User-Defined Attributes:**

• Example: Enumerated encoding.

A popular user-defined attribute, which is provided by synthesis tool vendors, is the enum\_encoding attribute. By default, enumerated data types are encoded sequentially. Thus, if we consider the enumerated data type color shown below:

```

TYPE color IS (red, green, blue, white);

```

its states will be encoded as red = "00", green = "01", blue = "10", and white = "11". Enum\_encoding allows the default encoding (sequential) to be changed. Thus the following encoding scheme could be employed, for example:

```

ATTRIBUTE enum_encoding OF color: TYPE IS "11 00 10 01";

```

Amin Mehranzadeh, Ph.D.

# **Operator Overloading:**

- using the BEGIN operators, same name as the predefined ones.

- new kind of addition, \_\_\_\_\_ technique is called outp <= 3 + inp1 + inp2; operator overloading.

```

• We can define our own function "+" (a: INTEGER, b: BIT) RETURN INTEGER IS

IF (b='1') THEN RETURN a+1;

END "+":

• For example, we could ------

use "+" to indicate a A call to the function above could thus be the following:

(...)

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

### **GENERIC:**

- As the name suggests, GENERIC is a way of specifying a generic parameter (that is, a static parameter that can be easily modified and adapted to different applications).

- A GENERIC statement, when employed, must be declared in the ENTITY. The specified parameter will then be truly global (that is, visible to the whole design, including the ENTITY itself). Its syntax is shown below.

```

GENERIC (parameter_name : parameter_type := parameter_value);

```

Amin Mehranzadeh, Ph.D.

### **GENERIC:**

• Example: whenever n is found in the ENTITY itself or in the ARCHITECTURE (one or more) that follows, its value will be assumed to be 8.

```

ENTITY my_entity IS

GENERIC (n : INTEGER := 8);

PORT (...);

END my_entity;

ARCHITECTURE my_architecture OF my_entity IS

...

END my_architecture:

More than one GENERIC parameter can be specified in an ENTITY. For example:

GENERIC (n: INTEGER := 8; vector: BIT_VECTOR := "00001111");

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

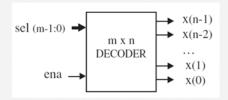

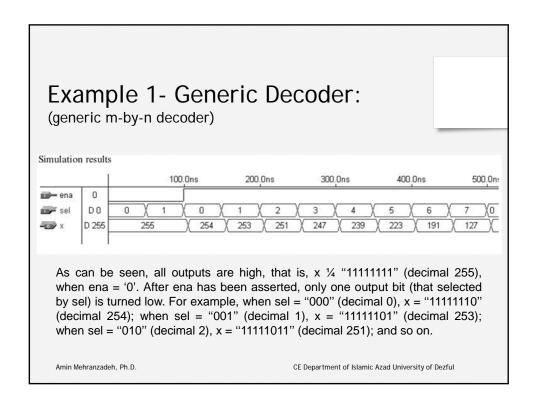

# Example 1- Generic Decoder:

(generic m-by-n decoder)

The circuit has two inputs, sel (m bits) and ena (single bit), and one output, x (n bits). We assume that n is a power of two, so m = log2n. If ena = '0', then all bits of x should be high; otherwise, the output bit selected by sel should be low.

| ena | sel | х    |

|-----|-----|------|

| 0   | 00  | 1111 |

| 1   | 00  | 1110 |

|     | 01  | 1101 |

|     | 10  | 1011 |

|     | 11  | 0111 |

Amin Mehranzadeh, Ph.D.

# Example 1- Generic Decoder:

(generic m-by-n decoder)

```

2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

5 ENTITY decoder IS

PORT ( ena : IN STD LOGIC;

7

sel : IN STD LOGIC VECTOR (2 DOWNTO 0);

x : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

8

11 ARCHITECTURE generic decoder OF decoder IS

12 BEGIN

13

PROCESS (ena, sel)

VARIABLE temp1 : STD_LOGIC_VECTOR (x'HIGH DOWNTO 0);

14

VARIABLE temp2 : INTEGER RANGE 0 TO x'HIGH;

15

BEGIN

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

### Example 1- Generic Decoder:

(generic m-by-n decoder)

```

temp1 := (OTHERS => '1');

17

18

temp2 := 0;

IF (ena='1') THEN

19

FOR i IN sel'RANGE LOOP -- sel range is 2 downto 0

IF (sel(i)='1') THEN -- Bin-to-Integer conversion

temp2:=2*temp2+1;

ELSE

temp2 := 2*temp2;

24

END IF;

25

END LOOP;

26

27

temp1(temp2):='0';

END IF;

28

x \le temp1;

30

END PROCESS;

31 END generic_decoder;

32 -----

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

14

```

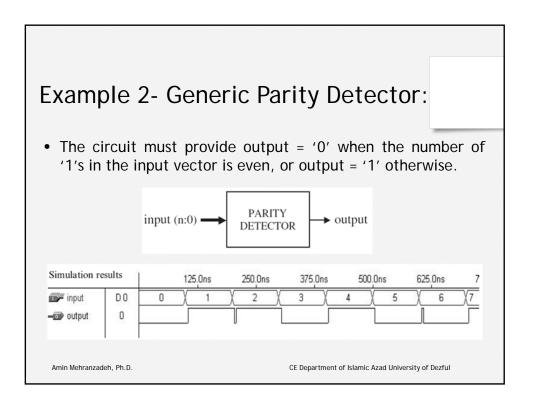

Example 2:

ENTITY parity_det IS

(Generic Parity Detector)<sup>2</sup>

GENERIC (n : INTEGER := 7);

4

PORT ( input: IN BIT_VECTOR (n DOWNTO 0);

5

output: OUT BIT);

6 END parity_det;

8 ARCHITECTURE parity OF parity_det IS

10

PROCESS (input)

VARIABLE temp: BIT;

11

12

BEGIN

13

temp := '0';

14

FOR i IN input'RANGE LOOP

temp := temp XOR input(i);

15

END LOOP;

16

17

output <= temp;

END PROCESS;

19 END parity;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

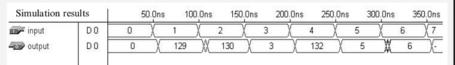

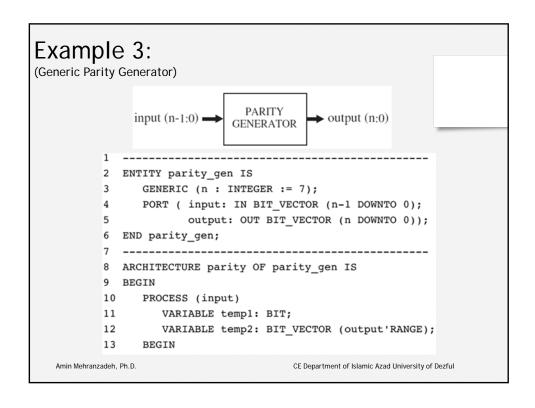

# **Example3-Generic Parity Generator:**

• The circuit must add one bit to the input vector (on its left). Such bit must be a '0' if the number of '1's in the input vector is even, or a '1' if it is odd, such that the resulting vector will always contain an even number of '1's (even parity).

when input ="0000000" (decimal 0, with seven bits), output = "00000000" (decimal 0, with eight bits); when input = "0000001" (decimal 1, with seven bits), output = "10000001" (decimal 129, with eight bits); and so on.

Amin Mehranzadeh, Ph.D.

```

Example 3:

(Generic Parity Generator)

13

BEGIN

temp1 := '0';

15

FOR i IN input'RANGE LOOP

16

temp1 := temp1 XOR input(i);

temp2(i) := input(i);

17

18

END LOOP;

19

temp2(output'HIGH) := temp1;

output <= temp2;</pre>

20

21

END PROCESS;

22 END parity;

23 -----

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

# Summary:

A summary of VHDL operators and attributes is presented in tables 4.1 and 4.2, respectively. The constructs that are not synthesizable (or have little synthesis support) are marked with the "→" symbol.

| Table 4.1 Operators. |                                       |                                                                                   |

|----------------------|---------------------------------------|-----------------------------------------------------------------------------------|

| Operator type        | Operators                             | Data types                                                                        |

| Assignment           | <=, :=, =>                            | Any                                                                               |

| Logical              | NOT, AND, NAND,<br>OR, NOR, XOR, XNOR | BIT, BIT_VECTOR,<br>STD_LOGIC, STD_LOGIC_VECTOR,<br>STD_ULOGIC, STD_ULOGIC_VECTOR |

| Arithmetic           | +, -, *, /, **<br>(mod, rem, abs)*    | INTEGER, SIGNED, UNSIGNED                                                         |

| Comparison           | =, /=, <, >, <=, >=                   | All above                                                                         |

| Shift                | sll, srl, sla, sra, rol, ror          | BIT_VECTOR                                                                        |

| Concatenation        | &, (,,,)                              | Same as for logical operators, plus SIGNED and UNSIGNED                           |

| Amin Mehranzadeh, Ph | n.D.                                  | CE Department of Islamic Azad University of Dezful                                |

# Summary:

| Ta  | ble  | 4. | 2   |

|-----|------|----|-----|

| Att | trib | ut | es. |

| Application      | Attributes                      | Return value                                             |  |

|------------------|---------------------------------|----------------------------------------------------------|--|

| For regular DATA | d'LOW                           | Lower array index                                        |  |

|                  | d'HIGH                          | Upper array index                                        |  |

|                  | d'LEFT                          | Leftmost array index                                     |  |

|                  | d'RIGHT                         | Rightmost array index                                    |  |

|                  | d'LENGTH                        | Vector size                                              |  |

|                  | d'RANGE                         | Vector range                                             |  |

|                  | d'REVERSE_RANGE                 | Reverse vector range                                     |  |

| For enumerated   | d'VAL(pos) <sup>♦</sup>         | Value in the position specified                          |  |

| DATA             | d'POS(value)◆                   | Position of the value specified                          |  |

|                  | d'LEFTOF(value) <sup>♦</sup>    | Value in the position to the left of the value specified |  |

|                  | d'VAL(row, column) <sup>♦</sup> | Value in the position specified                          |  |

| For a SIGNAL     | s'EVENT                         | True when an event occurs on s                           |  |

|                  | s'STABLE                        | True if no event has occurred on s                       |  |

|                  | s'ACTIVE*                       | True if s is high                                        |  |

Amin Mehranzadeh, Ph.D.