# Design with Hardware Description Languages (HDL)

(DHDL-94952)

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

mehranzadeh@iaud.ac.ir Mehran.students@gmail.com

# Concurrent Code

Amin Mehranzadeh, Ph.D.

#### Concurrent Code:

VHDL code can be concurrent (parallel) or sequential. The concurrent statements in VHDL are WHEN and GENERATE. Besides them, assignments using only operators (AND, NOT, +, \*, sll, etc.) can also be used to construct concurrent code. Finally, a special kind of assignment, called <u>BLOCK</u>, can also be employed in this kind of code.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

## Combinational versus Sequential Logic:

Combinational logic is that in which the output of the circuit depends solely on the current inputs and the system requires no memory and can be implemented using conventional logic gates.

Amin Mehranzadeh, Ph.D.

# Combinational versus Sequential Logic:

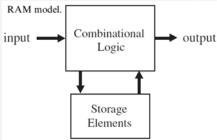

In Sequential logic, the output is depended on previous inputs. Therefore, storage elements are required, which are connected to the combinational logic block through a feedback loop.

present state

Combinational Logic

next state

Storage Elements

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Combinational versus Sequential Logic:

A common mistake is to think that any circuit that possesses storage elements (flip-flops) is sequential. A RAM (Random Access Memory) is an example (the storage elements appear in a forward path rather than in a feedback loop).

Amin Mehranzadeh, Ph.D.

# Concurrent versus Sequential Code:

VHDL code is inherently concurrent (parallel).

Only statements placed inside a PROCESS,

FUNCTION, or PROCEDURE are sequential.

Concurrent code is also called dataflow code.

Example: let us consider a code with three concurrent statements (stat1,stat2, stat3).

the order does not matter.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Concurrent versus Sequential Code:

- Concurrent code <u>can not</u> be used to implement <u>synchronous circuits</u> (the only exception is when a GUARDED BLOCK is used). In other words, in general we can only build combinational logic circuits with concurrent code.

- To obtain sequential logic circuits, sequential code must be employed.

Amin Mehranzadeh, Ph.D.

# Concurrent versus Sequential Code:

- in concurrent code the following can be used:

- Operators;

- The WHEN statement: (WHEN/ELSE or WITH/SELECT/WHEN);

- The GENERATE statement;

- The BLOCK statement.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

### Operators:

• This is the most basic way of creating concurrent code. Operators (AND, OR, +, -,\*, sII, sra, etc.):

| Operators.    |                                       |                                                                                   |  |  |  |  |

|---------------|---------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| Operator type | Operators                             | Data types                                                                        |  |  |  |  |

| Logical       | NOT, AND, NAND,<br>OR, NOR, XOR, XNOR | BIT, BIT_VECTOR,<br>STD_LOGIC, STD_LOGIC_VECTOR,<br>STD_ULOGIC, STD_ULOGIC_VECTOR |  |  |  |  |

| Arithmetic    | +, -, *, /, **<br>(mod, rem, abs)     | INTEGER, SIGNED, UNSIGNED                                                         |  |  |  |  |

| Comparison    | =, /=, <, >, <=, >=                   | All above                                                                         |  |  |  |  |

| Shift         | sll, srl, sla, sra, rol, ror          | BIT_VECTOR                                                                        |  |  |  |  |

| Concatenation | &, (,,,)                              | Same as for logical operators, plus SIGNED and UNSIGNED                           |  |  |  |  |

Amin Mehranzadeh, Ph.D.

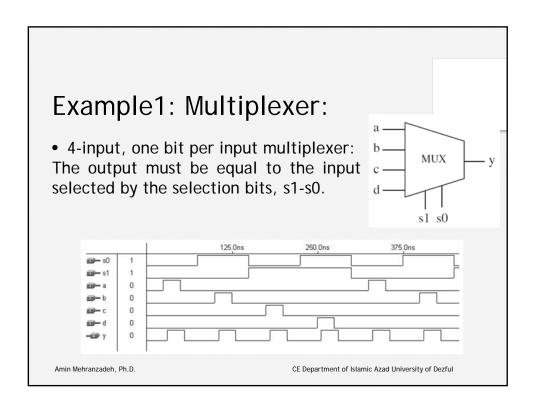

#### Example1: Multiplexer: Its implementation, 2 LIBRARY ieee; using only logical 3 USE ieee.std\_logic\_1164.all; operators, can be 4 done as follows: 5 ENTITY mux IS 6 PORT ( a, b, c, d, s0, s1: IN STD\_LOGIC; 7 y: OUT STD\_LOGIC); 8 END mux; 10 ARCHITECTURE pure logic OF mux IS 12 y <= (a AND NOT s1 AND NOT s0) OR (b AND NOT s1 AND s0) OR 13 (c AND s1 AND NOT s0) OR (d AND s1 AND s0); 16 END pure\_logic; Amin Mehranzadeh, Ph.D. CE Department of Islamic Azad University of Dezful

#### WHEN (Simple and Selected):

WHEN is one of the fundamental concurrent statements (along with operators and GENERATE). It appears in two forms: <u>WHEN / ELSE (simple WHEN)</u> and <u>WITH / SELECT / WHEN (selected WHEN)</u>. Its syntax is shown below.

```

assignment WHEN condition ELSE assignment WHEN condition ELSE WHEN / ELSE:

WITH identifier SELECT assignment WHEN value, assignment WHEN value, assignment WHEN value,

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

### WHEN (Simple and Selected):

Whenever WITH / SELECT / WHEN is used, all permutations must be tested, so the keyword OTHERS is often useful. Another important keyword is UNAFFECTED, which should be used when no action is to take place.

```

Example:

----- With WHEN/ELSE ------

outp <= "000" WHEN (inp='0' OR reset='1') ELSE

"001" WHEN ctl='1' ELSE

"010";

---- With WITH/SELECT/WHEN ------

WITH control SELECT

output <= "000" WHEN reset,

"111" WHEN set,

UNAFFECTED WHEN OTHERS;

Amin Mehranzadeh, Ph.D. CE Department of Islamic Azad University of Dezful

```

### WHEN (Simple and Selected):

Another important aspect related to the WHEN statement is that the "WHEN value" shown in the syntax above can indeed take up three forms:

```

WHEN value -- single value

WHEN value1 to value2 -- range, for enumerated data types

-- only

WHEN value1 | value2 | ... -- value1 or value2 or ...

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

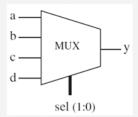

# Example 2: Multiplexer #2

- This example shows the implementation of the same multiplexer of example 1. However, in it <u>WHEN</u> was employed instead of <u>logical operators</u>. Two solutions are presented:

- using WHEN/ELSE (simple WHEN)

- using WITH/SELECT/WHEN (selected WHEN).

Amin Mehranzadeh, Ph.D.

# Example 2: Multiplexer #2

```

1 ----- Solution 1: with WHEN/ELSE -----

2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

4 -----

5 ENTITY mux IS

PORT ( a, b, c, d: IN STD_LOGIC;

7

sel: IN STD_LOGIC_VECTOR (1 DOWNTO 0);

8

y: OUT STD_LOGIC);

9 END mux;

11 ARCHITECTURE mux1 OF mux IS

y <= a WHEN sel="00" ELSE

b WHEN sel="01" ELSE

c WHEN sel="10" ELSE

15

17 END mux1;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

```

Example 2: Multiplexer #2

1 --- Solution 2: with WITH/SELECT/WHEN ----

2 LIBRARY ieee;

3 USE ieee.std logic 1164.all;

4 -----

5 ENTITY mux IS

PORT ( a, b, c, d: IN STD_LOGIC;

sel: IN STD LOGIC VECTOR (1 DOWNTO 0);

y: OUT STD_LOGIC);

9 END mux:

11 ARCHITECTURE mux2 OF mux IS

12 BEGIN

13 WITH sel SELECT

y \le a WHEN "00",

-- notice "," instead of ";"

15

b WHEN "01",

c WHEN "10",

16

d WHEN OTHERS;

-- cannot be "d WHEN "11" "

17

18 END mux2;

19 -----

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

```

Example 2: Multiplexer #2 2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

In the solutions

above, sel could have 5 ENTITY mux IS

been declared as an 6

PORT ( a, b, c, d: IN STD_LOGIC;

sel: IN INTEGER RANGE 0 TO 3;

INTEGER, in which

y: OUT STD_LOGIC);

case the code would 8

9 END mux;

be the following:

10 ---- Solution 1: with WHEN/ELSE -----

11 ARCHITECTURE mux1 OF mux IS

12 BEGIN

y <= a WHEN sel=0 ELSE

14

b WHEN sel=1 ELSE

c WHEN sel=2 ELSE

15

16

d;

17 END mux1;

18 -- Solution 2: with WITH/SELECT/WHEN -----

19 ARCHITECTURE mux2 OF mux IS

20 BEGIN

21 WITH sel SELECT

y \le a WHEN 0,

22

23

b WHEN 1,

c WHEN 2,

24

25

d WHEN 3;

-- here, 3 or OTHERS are equivalent,

26 END mux2;

-- for all options are tested anyway

CE Department of Islamic Azad University of Dezful

Amin Mehranzadeh, Ph.D.

```

Amin Mehranzadeh, Ph.D. CE Department of Islamic Azad University of Dezful

ena input

D O D Z

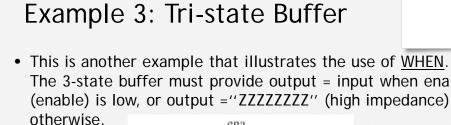

### Example 3: Tri-state Buffer

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

## Example 4: Encoder

(n-by-m encoder)

We assume that n is a power of two, so m = log2n. One and only one input bit is expected to be high at a time, whose address must be encoded at the output. Two solutions are presented, one using WHEN / ELSE, and the other with WITH / SELECT / WHEN.

Amin Mehranzadeh, Ph.D.

```

Example 4: Encoder

1 ---- Solution 1: with WHEN/ELSE -----

(n-by-m encoder)

2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

-----

5 ENTITY encoder IS

PORT ( x: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR (2 DOWNTO 0));

8 END encoder;

10 ARCHITECTURE encoder1 OF encoder IS

11 BEGIN

12

y <=

"000" WHEN x="0000001" ELSE

13

"001" WHEN x="00000010" ELSE

14

"010" WHEN x="00000100" ELSE

15

"011" WHEN x="00001000" ELSE

"100" WHEN x="00010000" ELSE

16

"101" WHEN x="00100000" ELSE

17

18

"110" WHEN x="01000000" ELSE

"111" WHEN x="10000000" ELSE

19

"ZZZ";

20

21 END encoder1;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

```

Example 4: Encoder

1 ---- Solution 2: with WITH/SELECT/WHEN -----

(n-by-m encoder)

2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

5 ENTITY encoder IS

PORT ( x: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR (2 DOWNTO 0));

8 END encoder;

10 ARCHITECTURE encoder2 OF encoder IS

12

WITH x SELECT

y <= "000" WHEN "0000001",

13

"001" WHEN "00000010",

14

"010" WHEN "00000100",

15

"011" WHEN "00001000",

16

"100" WHEN "00010000",

18

"101" WHEN "00100000",

19

"110" WHEN "01000000",

"111" WHEN "10000000",

20

21

"ZZZ" WHEN OTHERS;

22 END encoder2;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

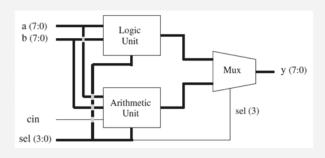

### Example 5: ALU

(Arithmetic Logic Unit)

ALU is a circuit capable of executing both kinds of operations, arithmetic as well as logical.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

# Example 5: ALU

(Arithmetic Logic Unit)

• The output (arithmetic or logical) is selected by the MSB of sel, while the specific operation is selected by sel's other three bits.

Sel Operation Function Unit

| sel  | Operation     | Function               | Unit       |

|------|---------------|------------------------|------------|

| 0000 | y <= a        | Transfer a             |            |

| 0001 | y <= a+1      | Increment a            |            |

| 0010 | y <= a-1      | Decrement a            |            |

| 0011 | y <= b        | Transfer b             | Arithmetic |

| 0100 | y <= b+1      | Increment b            |            |

| 0101 | y <= b-1      | Decrement b            |            |

| 0110 | y <= a+b      | Add a and b            |            |

| 0111 | y <= a+b+cin  | Add a and b with carry |            |

| 1000 | y <= NOT a    | Complement a           |            |

| 1001 | y <= NOT b    | Complement b           |            |

| 1010 | y <= a AND b  | AND                    |            |

| 1011 | y <= a OR b   | OR                     | Logic      |

| 1100 | y <= a NAND b | NAND                   |            |

| 1101 | y <= a NOR b  | NOR                    |            |

| 1110 | y <= a XOR b  | XOR                    |            |

| 1111 | y <= a XNOR b | XNOR                   |            |

Amin Mehranzadeh, Ph.D.

```

Example 5: ALU

1

(Arithmetic Logic Unit)

2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

4 USE ieee.std_logic_unsigned.all;

ENTITY ALU IS

7

PORT (a, b: IN STD_LOGIC_VECTOR (7 DOWNTO 0);

sel: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

8

9

cin: IN STD_LOGIC;

10

y: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

11 END ALU;

12 -----

13 ARCHITECTURE dataflow OF ALU IS

14 SIGNAL arith, logic: STD_LOGIC_VECTOR (7 DOWNTO 0);

15 BEGIN

16

---- Arithmetic unit: -----

WITH sel(2 DOWNTO 0) SELECT

17

18

arith <= a WHEN "000",

19

a+1 WHEN "001",

a-1 WHEN "010",

20

b WHEN "011",

21

b+1 WHEN "100",

22

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

```

Example 5: ALU

(Arithmetic Logic Unit)

23

b-1 WHEN "101",

a+b WHEN "110",

24

25

a+b+cin WHEN OTHERS;

---- Logic unit: -----

26

WITH sel(2 DOWNTO 0) SELECT

27

28

logic <= NOT a WHEN "000",

29

NOT b WHEN "001",

30

a AND b WHEN "010",

31

a OR b WHEN "011",

32

a NAND b WHEN "100",

a NOR b WHEN "101",

33

34

a XOR b WHEN "110",

35

NOT (a XOR b) WHEN OTHERS;

36

----- Mux: -----

37

WITH sel(3) SELECT

y <= arith WHEN '0',

38

39

logic WHEN OTHERS;

40 END dataflow;

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

```

#### **GENERATE:**

GENERATE is another concurrent statement (along with operators and WHEN). It is equivalent to the sequential statement LOOP in the sense that it allows a section of code to be repeated a number of times, thus creating several instances of the same assignments. Its regular form is the FOR / GENERATE construct. Notice that GENERATE must be labeled.

FOR / GENERATE:

```

label: FOR identifier IN range GENERATE

(concurrent assignments)

END GENERATE;

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **GENERATE:**

An irregular form is also available, which uses IF/GENERATE (with an IF equivalent; recall that originally IF is a sequential statement). Here ELSE is not allowed. In the same way that IF/GENERATE can be nested inside FOR/GENERATE (syntax below), the opposite can also be done.

IF / GENERATE nested inside FOR / GENERATE:

```

label1: FOR identifier IN range GENERATE

...

label2: IF condition GENERATE

(concurrent assignments)

END GENERATE;

...

END GENERATE;

```

Amin Mehranzadeh, Ph.D.

#### **GENERATE:**

```

Example:

SIGNAL x: BIT_VECTOR (7 DOWNTO 0);

SIGNAL y: BIT_VECTOR (15 DOWNTO 0);

SIGNAL z: BIT_VECTOR (7 DOWNTO 0);

...

G1: FOR i IN x'RANGE GENERATE

z(i) <= x(i) AND y(i+8);

END GENERATE;

```

One important remark about GENERATE (and the same is true for LOOP) is that both limits of the range must be static. As an example, let us consider the code below, where choice is an input (non-static) parameter. This kind of code is generally not synthesizable.

```

NotOK: FOR i IN 0 TO choice GENERATE (concurrent statements)

END GENERATE;

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

CE Department of Islamic Azad University of Dezful

#### **GENERATE:**

Amin Mehranzadeh, Ph.D.

We also must to be aware of multiply-driven (unresolved) signals. For example,

```

OK: FOR i IN 0 TO 7 GENERATE

output(i)<='1' WHEN (a(i) AND b(i))='1' ELSE '0';

END GENERATE;

```

is fine. However, the compiler will complain that "accum" is multiply driven (and stop compilation) in either of the following two cases:

```

NotOK: FOR i IN 0 TO 7 GENERATE

accum <="11111111" WHEN (a(i) AND b(i))='1' ELSE "00000000";

END GENERATE;

NotOK: For i IN 0 to 7 GENERATE

accum <= accum + 1 WHEN x(i)='1';

END GENERATE;

```

#### Example 6: Vector Shifter

This example illustrates the use of GENERATE. In it, the output vector must be a shifted version of the input vector. For example, if the input bus has width 4, and the present value is "1111", then the output should be one of the lines of the following matrix (the original vector is underscored):

row(1): 0 0 0 1 1 1 1 0 0 row(2): 0 0 1 1 1 1 1 0 0 0 row(3): 0 1 1 1 1 0 0 0 0 row(4): 1 1 1 1 1 0 0 0 0

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

## Example 6: Vector Shifter

```

1 -----

2 LIBRARY ieee;

3 USE ieee.std_logic_1164.all;

5 ENTITY shifter IS

PORT ( inp: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

6

sel: IN INTEGER RANGE 0 TO 4;

7

outp: OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

8

9 END shifter;

11 ARCHITECTURE shifter OF shifter IS

12 SUBTYPE vector IS STD_LOGIC_VECTOR (7 DOWNTO 0);

TYPE matrix IS ARRAY (4 DOWNTO 0) OF vector;

13

14

SIGNAL row: matrix;

15 BEGIN

```

Amin Mehranzadeh, Ph.D.

#### Example 6: Vector Shifter

As can be seen, inp = "0011" (decimal 3) was applied to the circuit. The result was outp = "00000011" (decimal 3) when sel = 0 (no shift), outp = "00000110" (decimal 6) when sel = 1 (one shift to the left), outp = "00001100" (decimal 12) when sel = 2 (two shifts to the left), and so on.

|         |    | 100.0ns | 200.0ns | 300.0ns | 400.0ns | 500.0ns | 600.0ns | 700.0ns | 800.0r |

|---------|----|---------|---------|---------|---------|---------|---------|---------|--------|

| inp inp | D3 |         |         |         | 3       |         |         |         |        |

| sel     | D0 | 0       | 1       | $\chi$  | 2       | 3       | $\chi$  | 4       | 5      |

| outp    | D3 | 3       | 6       | $-\chi$ | 12      | 24      | $-\chi$ | 48      | V 0    |

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **BLOCK:**

(There are two kinds of BLOCK statements: Simple and Guarded)

#### • Simple BLOCK:

The BLOCK statement, in its simple form, represents only a way of locally partitioning the code. It allows a set of concurrent statements to be clustered into a BLOCK, with the purpose of turning the overall code <u>more readable</u> and <u>more manageable</u> (which might be helpful when dealing with long codes). Its syntax is shown below.

```

label: BLOCK

[declarative part]

BEGIN

(concurrent statements)

END BLOCK label;

```

Amin Mehranzadeh, Ph.D.

#### **BLOCK:** (There are two kinds of BLOCK statements: Simple and Guarded) • Simple BLOCK: ARCHITECTURE example ... Therefore, the overall aspect of a BEGIN "blocked" code is the following: block1: BLOCK BEGIN Example: END BLOCK block1 b1: BLOCK block2: BLOCK SIGNAL a: STD\_LOGIC; BEGIN a <= input\_sig WHEN ena='1' ELSE 'Z'; END BLOCK block2; END BLOCK b1; END example;

#### **BLOCK:**

Amin Mehranzadeh, Ph.D.

(There are two kinds of BLOCK statements: Simple and Guarded)

A BLOCK (simple or guarded) can be nested inside another BLOCK. The corresponding syntax is shown below.

```

label1: BLOCK

[declarative part of top block]

BEGIN

[concurrent statements of top block]

label2: BLOCK

[declarative part nested block]

BEGIN

(concurrent statements of nested block)

END BLOCK label2;

[more concurrent statements of top block]

END BLOCK label1;

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

#### **BLOCK:**

(There are two kinds of BLOCK statements: Simple and Guarded)

Guarded BLOCK:

A guarded BLOCK is a special kind of BLOCK, which includes an additional expression, called guard expression. A guarded statement in a guarded BLOCK is executed only when the guard expression is TRUE.

#### Guarded BLOCK:

```

label: BLOCK (guard expression)

[declarative part]

(concurrent guarded and unguarded statements)

END BLOCK label;

```

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

### Example 7:

#### Latch Implemented with a Guarded BLOCK

• The example presented 2 LIBRARY ieee; below clk='1' (line12) is the guard expression, while 7 q<=GUARDED d (line 14) 8 END latch;</pre> is a guarded statement. Therefore, q<=d will only occur if clk='1'.

```

implements a 3 USE ieee.std_logic_1164.all;

transparent latch. In it,

5 ENTITY latch IS

6 PORT (d, clk: IN STD_LOGIC;

q: OUT STD_LOGIC);

10 ARCHITECTURE latch OF latch IS

11 BEGIN

12 b1: BLOCK (clk='1')

13 BEGIN

q <= GUARDED d;

15 END BLOCK b1;

16 END latch;

CE Department of Islamic Azad University of Dezful

```

Amin Mehranzadeh, Ph.D.

## Example 8:

#### DFF Implemented with a Guarded BLOCK

A positive-edge sensitive 2 LIBRARY ieee; expression, while q <= 8 END dff; statement. q<='0' will occur when the 12 BEGIN guard expression is true 14 and rst is '1'.

```

D-type flip-flop, with 3 USE ieee.std_logic_1164.all;

synchronous reset. In it, 4 ------

clk'EVENT AND clk='1'

(line 12) is the guard

Sentity dff is

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

q: OUT STD_LOGIC);

GUARDED '0' WHEN rst='1' 9 ------

(line 14) is a guarded ^{10} ARCHITECTURE dff of dff is

Therefore, 11 BEGIN 12 b1: BLOCK (clk'EVENT AND clk='1')

q <= GUARDED '0' WHEN rst='1' ELSE d;

15 END BLOCK b1;

16 END dff;

```

Amin Mehranzadeh, Ph.D.