- As mentioned before, VHDL code is inherently concurrent. PROCESSES, FUNCTIONS, and PROCEDURES are the only sections of code that are executed sequentially. However, as a whole, any of these blocks is still concurrent with any other statements placed outside it.

- Sequential code is also called behavioral code.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

## PROCESS:

• Its syntax is shown below:

```

[label:] PROCESS (sensitivity list)

[VARIABLE name type [range] [:= initial_value;]]

BEGIN

(sequential code)

END PROCESS [label];

```

## Notes:

- VARIABLES are optional. If used, they must be declared in the declarative part of the PROCESS (before the word BEGIN, as indicated in the syntax above).

- The initial value is not synthesizable, being only taken into consideration in simulations.

- The use of a label is also optional. Its purpose is to improve code readability. The label can be any word, except VHDL reserved words.

Amin Mehranzadeh, Ph.D.

CE Department of Islamic Azad University of Dezful

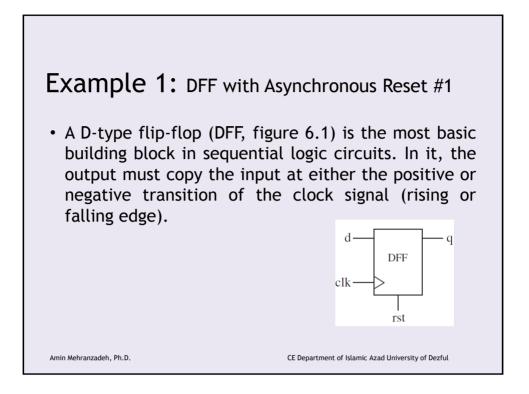

| Example 1: DFF with Asynchronous Reset #1 |                                                                           |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------|--|--|--|

|                                           | <pre>1 2 LIBRARY ieee; 3 USE ieee.std_logic_1164.all; 4</pre>             |  |  |  |

|                                           | 5 ENTITY dff IS<br>6 PORT (d, clk, rst: IN STD_LOGIC;                     |  |  |  |

|                                           | 7 q: OUT STD_LOGIC);<br>8 END dff;<br>9                                   |  |  |  |

|                                           | 10 ARCHITECTURE behavior OF dff IS<br>11 BEGIN                            |  |  |  |

|                                           | 12 PROCESS (clk, rst)<br>13 BEGIN                                         |  |  |  |

|                                           | 14 IF (rst='1') THEN<br>15 q <= '0';                                      |  |  |  |

|                                           | <pre>16 ELSIF (clk'EVENT AND clk='1') THEN 17 q &lt;= d; 18 END IF;</pre> |  |  |  |

|                                           | 19 END PROCESS;<br>20 END behavior;                                       |  |  |  |

| Amin Mehranzadeh, Ph.D.                   | 21                                                                        |  |  |  |

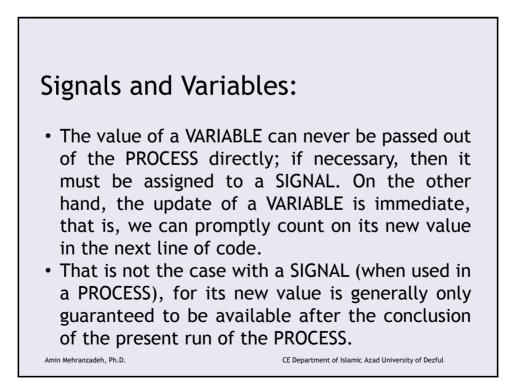

- VHDL has two ways of passing non-static values around: by means of a SIGNAL or by means of a VARIABLE.

- A SIGNAL can be declared in a PACKAGE, ENTITY or ARCHITECTURE (in its declarative part), while a VARIABLE can only be declared inside a piece of sequential code (in a PROCESS, for example).

- Therefore, while the value of the former can be global, the latter is always local.

Amin Mehranzadeh, Ph.D

```

CE Department of Islamic Azad University of Dezful

```

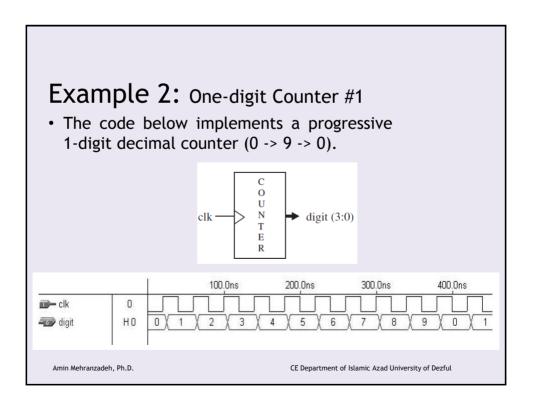

| Example 2: One-digit Counter #1 |                                                 |  |  |  |

|---------------------------------|-------------------------------------------------|--|--|--|

|                                 | 1                                               |  |  |  |

|                                 | 2 LIBRARY ieee;                                 |  |  |  |

|                                 | 3 USE ieee.std_logic_1164.all;                  |  |  |  |

|                                 | 4                                               |  |  |  |

|                                 | 5 ENTITY counter IS                             |  |  |  |

|                                 | <pre>6 PORT (clk : IN STD_LOGIC;</pre>          |  |  |  |

|                                 | <pre>7 digit : OUT INTEGER RANGE 0 TO 9);</pre> |  |  |  |

|                                 | 8 END counter;                                  |  |  |  |

|                                 | 9                                               |  |  |  |

|                                 | 10 ARCHITECTURE counter OF counter IS           |  |  |  |

|                                 | 11 BEGIN                                        |  |  |  |

|                                 | 12 count: PROCESS(clk)                          |  |  |  |

|                                 | 13 VARIABLE temp : INTEGER RANGE 0 TO 10;       |  |  |  |

|                                 | 14 BEGIN                                        |  |  |  |

|                                 | 15 IF (clk'EVENT AND clk='1') THEN              |  |  |  |

|                                 | 16 temp := temp + 1;                            |  |  |  |

|                                 | 17 IF (temp=10) THEN temp := 0;                 |  |  |  |

|                                 | 18 END IF;                                      |  |  |  |

|                                 | 19 END IF;                                      |  |  |  |

|                                 | <pre>20 digit &lt;= temp;</pre>                 |  |  |  |

|                                 | 21 END PROCESS count;                           |  |  |  |

| Amin Mehranzadeh, Ph.D.         | 22 END counter;                                 |  |  |  |

|                                 | 23                                              |  |  |  |

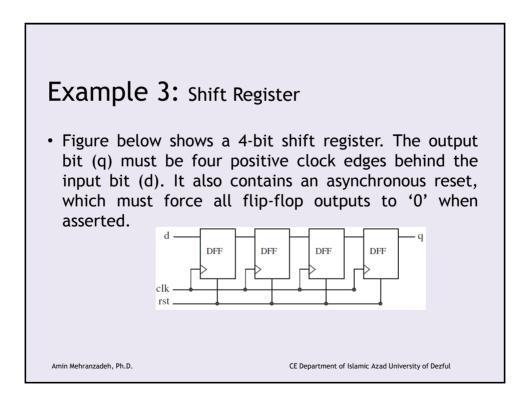

| Example 3               | 3: | Shift Register                                                      |

|-------------------------|----|---------------------------------------------------------------------|

| -                       | 1  |                                                                     |

|                         | 2  | LIBRARY ieee;                                                       |

|                         | 3  | USE ieee.std logic 1164.all;                                        |

|                         | 4  |                                                                     |

|                         | 5  | ENTITY shiftreg IS                                                  |

|                         | 6  | GENERIC (n: INTEGER := 4); # of stages                              |

|                         | 7  | PORT (d, clk, rst: IN STD_LOGIC;                                    |

|                         | 8  | q: OUT STD_LOGIC);                                                  |

|                         | 9  | END shiftreg;                                                       |

|                         | 10 |                                                                     |

|                         | 11 | ARCHITECTURE behavior OF shiftreg IS                                |

|                         | 12 | SIGNAL internal: STD_LOGIC_VECTOR (n-1 DOWNTO 0);                   |

|                         | 13 | BEGIN                                                               |

|                         | 14 | PROCESS (clk, rst)                                                  |

|                         | 15 | BEGIN                                                               |

|                         |    | IF (rst='1') THEN                                                   |

|                         | 17 | <pre>internal &lt;= (OTHERS =&gt; '0');</pre>                       |

|                         | 18 | ELSIF (clk'EVENT AND clk='1') THEN                                  |

|                         | 19 | <pre>internal &lt;= d &amp; internal(internal'LEFT DOWNTO 1);</pre> |

|                         | 20 | END IF;                                                             |

|                         |    | END PROCESS;                                                        |

|                         |    | <pre>q &lt;= internal(0);</pre>                                     |

| Amin Mehranzadeh, Ph.D. | 23 | END behavior;                                                       |

| , and anzaderi, The     | 24 |                                                                     |

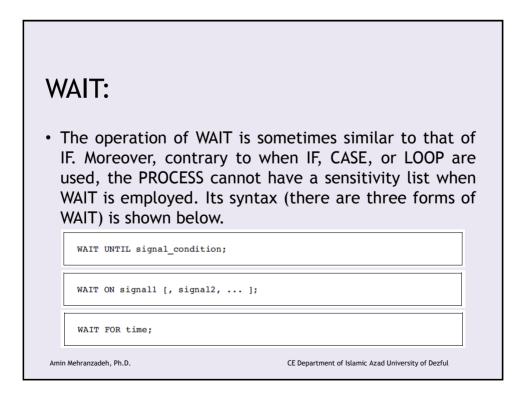

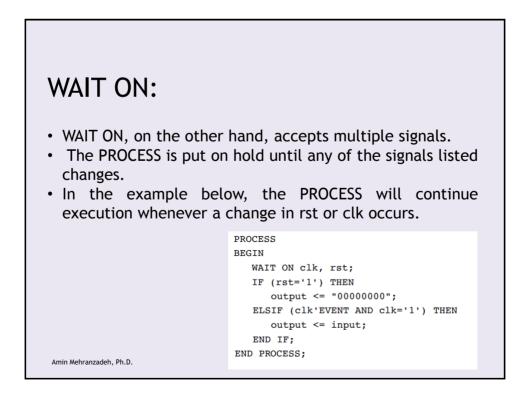

| WAIT UNTIL:                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                            |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| • The WAIT UNTIL statement accepts only one signal, thus<br>being more appropriate for synchronous code than<br>asynchronous. Since the PROCESS has no sensitivity list in<br>this case, WAIT UNTIL must be the first statement in the<br>PROCESS. The PROCESS will be executed every time the |                                                                                                                                                                                                            |  |  |  |

| condition is met. Example: 8-bit register with synchronous reset.                                                                                                                                                                                                                              |                                                                                                                                                                                                            |  |  |  |

|                                                                                                                                                                                                                                                                                                | <pre>PROCESS no sensitivity list<br/>BEGIN<br/>WAIT UNTIL (clk'EVENT AND clk='1');<br/>IF (rst='1') THEN<br/>output &lt;= "00000000";<br/>ELSIF (clk'EVENT AND clk='1') THEN<br/>output &lt;= input;</pre> |  |  |  |

| Amin Mehranzadeh, Ph.D.                                                                                                                                                                                                                                                                        | END IF;<br>END PROCESS;                                                                                                                                                                                    |  |  |  |

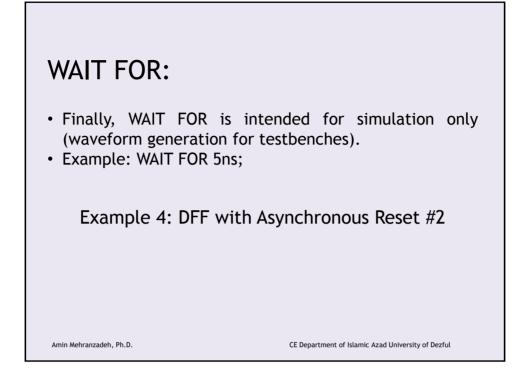

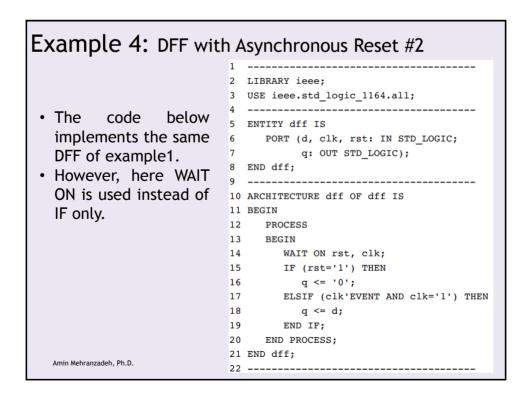

## Example 5: One-digit Counter #2

1 ----

2 LIBRARY ieee; 3 USE ieee.std\_logic\_1164.all; • The code below 4 -----5 ENTITY counter IS implements the same 6 PORT (clk : IN STD\_LOGIC; progressive 1-digit 7 digit : OUT INTEGER RANGE 0 TO 9); decimal counter of 8 END counter; example2. 9 -----• However, WAIT UNTIL 10 ARCHITECTURE counter OF counter IS 11 BEGIN was used instead of 12 PROCESS -- no sensitivity list IF only. 13 VARIABLE temp : INTEGER RANGE 0 TO 10; 14 BEGIN 15 WAIT UNTIL (clk'EVENT AND clk='1'); 16 temp := temp + 1; 17 IF (temp=10) THEN temp := 0; 18 END IF; 19 digit <= temp;</pre> 20 END PROCESS; 21 END counter; Amin Mehranzadeh, Ph.D. 22 -----

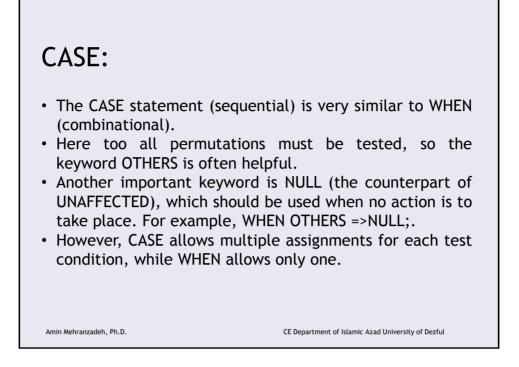

|                                                                                                 | atement intended exclusively for<br>ong with IF, LOOP, and WAIT). Its<br>/.                                                                                                         |  |  |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CASE identifier IS<br>WHEN value => assignments;<br>WHEN value => assignments;<br><br>END CASE; |                                                                                                                                                                                     |  |  |

| Amin Mehranzadeh, Ph.D.                                                                         | <pre>Example:<br/>CASE control IS<br/>WHEN "00" =&gt; x&lt;=a; y&lt;=b;<br/>WHEN "01" =&gt; x&lt;=b; y&lt;=c;<br/>WHEN OTHERS =&gt; x&lt;="0000"; y&lt;="ZZZZ";<br/>END CASE;</pre> |  |  |

| CACE.                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CASE:                                                                                                                                                                    |

| <ul> <li>Like in the case of WHEN, here too "WHEN value" can<br/>take up three forms:</li> </ul>                                                                         |

| WHEN value       single value         WHEN value1 to value2       range, for enumerated data types         only         WHEN value1   value2         value1 or value2 or |

|                                                                                                                                                                          |

| Amin Mehranzadeh, Ph.D. CE Department of Islamic Azad University of Dezful                                                                                               |

| Example 6: DFF with Asynchronous Reset #3                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <ul> <li>The code below<br/>implements the<br/>same DFF of<br/>example1.</li> <li>However, here<br/>CASE was used<br/>instead of IF<br/>only.</li> </ul> | 1<br>2 LIBRARY ieee; Unnecessary declaration,<br>3 because<br>4 USE ieee.std_logic_1164.all; BIT was used instead of<br>5<br>6<br>7 ENTITY dff IS<br>8 PORT (d, clk, rst: IN BIT;<br>9 q: OUT BIT);<br>10 END dff;<br>11<br>12 ARCHITECTURE dff3 OF dff IS<br>13 BEGIN<br>14 PROCESS (clk, rst)<br>15 BEGIN<br>16 CASE rst IS<br>17 WHEN '1' => q<='0';<br>18 WHEN '0' =><br>19 IF (clk'EVENT AND clk='1') THEN<br>20 q <= d;<br>21 END IF;<br>22 WHEN OTHERS => NULL; Unnecessary, rst is of type<br>3 BIT<br>24 END CASE; |  |  |  |  |

| Amin Mehranzadeh, Ph.D.                                                                                                                                  | 25 END PROCESS;<br>26 END dff3;<br>27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

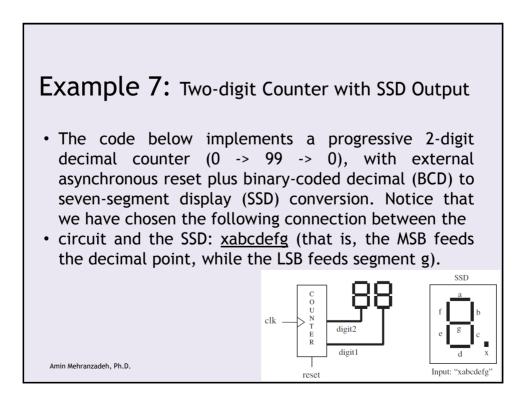

| Example 7               | : Two-digit Counter with SSD Output                             |

|-------------------------|-----------------------------------------------------------------|

| 1                       | LIBRARY ieee;                                                   |

| 3                       |                                                                 |

| 4                       |                                                                 |

|                         |                                                                 |

|                         | <pre>digit1, digit2 : OUT STD_LOGIC_VECTOR (6 DOWNTO 0));</pre> |

|                         | END counter;                                                    |

|                         | 0 ARCHITECTURE counter OF counter IS                            |

| 1                       | 1 BEGIN                                                         |

|                         | 2 PROCESS(clk, reset)                                           |

|                         | 3 VARIABLE temp1: INTEGER RANGE 0 TO 10;                        |

|                         | 4 VARIABLE temp2: INTEGER RANGE 0 TO 10;<br>5 BEGIN             |

| 1                       | 6 counter:                                                      |

| 1                       | 7 IF (reset='1') THEN                                           |

|                         | 8 temp1 := 0;<br>9 temp2 := 0;                                  |

|                         | 0 ELSIF (clk'EVENT AND clk='1') THEN                            |

| 2                       | <pre>temp1 := temp1 + 1;</pre>                                  |

|                         | 2 IF (temp1=10) THEN                                            |

|                         | <pre>13 temp1 := 0;<br/>14 temp2 := temp2 + 1;</pre>            |

|                         | 15 		IF (temp2=10) 	THEN                                        |

| Amin Mehranzadeh, Ph.D. | 6 temp2 := 0;                                                   |

| Example 7: Two-di       | igit (   | Counter with SSD Output                                              |

|-------------------------|----------|----------------------------------------------------------------------|

|                         | -        |                                                                      |

|                         | 27       | END IF;                                                              |

|                         | 28       | END IF;                                                              |

|                         | 29       | END IF;                                                              |

|                         | 30       | BCD to SSD conversion:                                               |

|                         | 31       | CASE temp1 IS                                                        |

|                         | 32       | WHEN 0 => digit1 <= "1111110";7E                                     |

|                         | 33       | WHEN 1 => digit1 <= "0110000";30                                     |

|                         | 34       | WHEN 2 => digit1 <= "1101101";6D                                     |

|                         | 35<br>36 | WHEN 3 => digit1 <= "1111001";79<br>WHEN 4 => digit1 <= "0110011";33 |

|                         | 36       | WHEN 4 => digit1 <= "0110011";33<br>WHEN 5 => digit1 <= "1011011";5B |

|                         | 38       | WHEN 5 => digit1 <= "1011011";5F                                     |

|                         | 39       | WHEN 6 => digit1 <= "1011111";5F<br>WHEN 7 => digit1 <= "1110000";70 |

|                         | 40       | WHEN 8 => digit1 <= "1110000";70<br>WHEN 8 => digit1 <= "1111111";7F |

|                         | 41       | WHEN 9 => digit1 <= "1111011";7B                                     |

|                         | 42       | WHEN OTHERS => NULL:                                                 |

|                         | 43       | END CASE;                                                            |

|                         | 44       | CASE temp2 IS                                                        |

|                         | 45       | WHEN 0 => digit2 <= "1111110";7E                                     |

|                         | 46       | WHEN 1 => digit2 <= "0110000";30                                     |

|                         | 47       | WHEN 2 => digit2 <= "1101101";6D                                     |

|                         | 48       | WHEN 3 => digit2 <= "1111001";79                                     |

|                         | 49       | WHEN 4 => digit2 <= "0110011";33                                     |

|                         | 50       | WHEN 5 => digit2 <= "1011011";5B                                     |

|                         | 51       | WHEN 6 => digit2 <= "1011111";5F                                     |

|                         | 52       | WHEN 7 => digit2 <= "1110000";70                                     |

|                         | 53       | WHEN 8 => digit2 <= "11111111";7F                                    |

|                         | 54       | WHEN 9 => digit2 <= "1111011";7B                                     |

|                         | 55       | WHEN OTHERS => NULL;                                                 |

|                         | 56       | END CASE;                                                            |

|                         | 57       | END PROCESS;                                                         |

| Amin Mehranzadeh, Ph.D. | 58 ENI   | D counter;                                                           |

|                         | 59       |                                                                      |

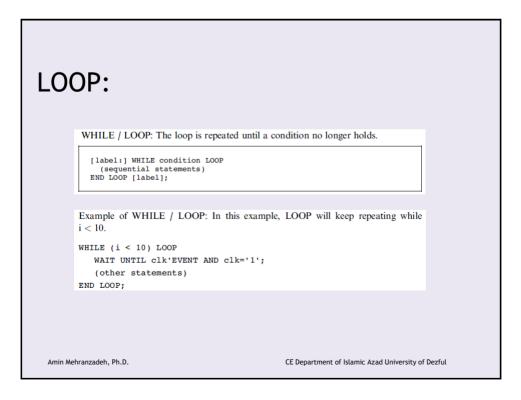

| <ul> <li>LOOP:</li> <li>As the name says, LOOP is umust be instantiated severation ways of using LOOP, as shown</li> </ul>                    | l times. There are several                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| FOR / LOOP: The loop is repeated a fixed n [label:] FOR identifier IN range LOOP (sequential statements) END LOOP [label];                    |                                                                                                                                    |

| Note:<br>One important remark regarding FOR / LOOP<br>(similar to that made for GENERATE) is that<br>both limits of the range must be static. | <pre>Example of FOR / LOOP:<br/>FOR i IN 0 TO 5 LOOP<br/>x(i) &lt;= enable AND w(i+2);<br/>y(0, i) &lt;= w(i);<br/>END LOOP;</pre> |

| Amin Mehranzadeh, Ph.D.                                                                                                                       | CE Department of Islamic Azad University of Dezful                                                                                 |

| LOOP:                   |                                                                    |                           |

|-------------------------|--------------------------------------------------------------------|---------------------------|

| EXIT: Used for e        | nding the loop.                                                    |                           |

| [label:] EXIT           | [label] [WHEN condition];                                          |                           |

| •                       | th EXIT: In this case, the loop<br>lue different from '0' is found |                           |

|                         | FOR i IN data'RANGE LOOP                                           |                           |

|                         | CASE data(i) IS                                                    |                           |

|                         | WHEN '0' => count:=count+1;                                        |                           |

|                         | WHEN OTHERS => EXIT;<br>END CASE;                                  |                           |

|                         | END LOOP;                                                          |                           |

|                         |                                                                    |                           |

| Amin Mehranzadeh, Ph.D. | CE Department of Islamic A                                         | azad University of Dezful |

| LO      | OP:                                                           |                                                        |  |

|---------|---------------------------------------------------------------|--------------------------------------------------------|--|

| NEX     | T: Used for skipping loop steps.                              |                                                        |  |

| [14     | abel:] NEXT [loop_label] [WHEN                                | condition];                                            |  |

|         | •                                                             | the example below, NEXT<br>ne iteration when i = skip. |  |

|         | FOR i IN 0 TO 15 LOOP<br>NEXT WHEN i=skip;<br>()<br>END LOOP; | jumps to next iteration                                |  |

| Amin Me | hranzadeh, Ph.D.                                              | CE Department of Islamic Azad University of Dezful     |  |

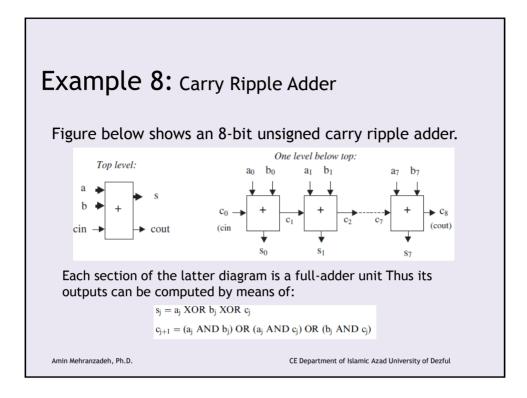

| Example 8:              | Carry Ripple Adder                                                 |  |  |  |

|-------------------------|--------------------------------------------------------------------|--|--|--|

| •                       | 1 Solution 1: Generic, with VECTORS                                |  |  |  |

|                         | LIBRARY ieee;                                                      |  |  |  |

|                         | USE ieee.std_logic_1164.all;                                       |  |  |  |

|                         |                                                                    |  |  |  |

|                         | 5 ENTITY adder IS                                                  |  |  |  |

|                         | <pre>6 GENERIC (length : INTEGER := 8);</pre>                      |  |  |  |

|                         | <pre>7 PORT ( a, b: IN STD_LOGIC_VECTOR (length-1 DOWNTO 0);</pre> |  |  |  |

|                         | 8 cin: IN STD_LOGIC;                                               |  |  |  |

|                         | <pre>9 s: OUT STD_LOGIC_VECTOR (length-1 DOWNTO 0);</pre>          |  |  |  |

|                         | 10 cout: OUT STD_LOGIC);                                           |  |  |  |

|                         | 11 END adder;                                                      |  |  |  |

|                         | 12                                                                 |  |  |  |

|                         | 13 ARCHITECTURE adder OF adder IS                                  |  |  |  |

|                         | 14 BEGIN                                                           |  |  |  |

|                         | 15 PROCESS (a, b, cin)                                             |  |  |  |

|                         | <pre>16 VARIABLE carry : STD_LOGIC_VECTOR (length DOWNTO 0);</pre> |  |  |  |

|                         | 17 BEGIN                                                           |  |  |  |

|                         | 18 carry(0) := cin;                                                |  |  |  |

|                         | 19 FOR i IN 0 TO length-1 LOOP                                     |  |  |  |

|                         | 20 s(i) <= a(i) XOR b(i) XOR carry(i);                             |  |  |  |

|                         | 21 carry(i+1) := (a(i) AND b(i)) OR (a(i) AND                      |  |  |  |

|                         | 22 carry(i)) OR (b(i) AND carry(i));                               |  |  |  |

|                         | 23 END LOOP;                                                       |  |  |  |

|                         | <pre>24 cout &lt;= carry(length);</pre>                            |  |  |  |

|                         | 25 END PROCESS;                                                    |  |  |  |

| Amin Mehranzadeh, Ph.D. | 26 END adder;                                                      |  |  |  |

|                         | 27                                                                 |  |  |  |

| Example 8: Carry Ripple Adder |    |                                         |  |  |

|-------------------------------|----|-----------------------------------------|--|--|

|                               | 1  | Solution 2: non-generic, with INTEGERS  |  |  |

|                               | 2  | LIBRARY ieee;                           |  |  |

|                               | 3  | USE ieee.std_logic_1164.all;            |  |  |

|                               | 4  |                                         |  |  |

|                               | 5  | ENTITY adder IS                         |  |  |

|                               | 6  | PORT ( a, b: IN INTEGER RANGE 0 TO 255; |  |  |

|                               | 7  | c0: IN STD_LOGIC;                       |  |  |

|                               | 8  | s: OUT INTEGER RANGE 0 TO 255;          |  |  |

|                               | 9  | c8: OUT STD_LOGIC);                     |  |  |

|                               | 10 | END adder;                              |  |  |

|                               | 11 |                                         |  |  |

|                               | 12 | ARCHITECTURE adder OF adder IS          |  |  |

|                               | 13 | BEGIN                                   |  |  |

|                               | 14 | PROCESS (a, b, c0)                      |  |  |

|                               | 15 | VARIABLE temp : INTEGER RANGE 0 TO 511; |  |  |

|                               | 16 | BEGIN                                   |  |  |

|                               | 17 | IF (c0='1') THEN temp:=1;               |  |  |

|                               | 18 | ELSE temp:=0;                           |  |  |

|                               | 19 | END IF;                                 |  |  |

|                               | 20 | <pre>temp := a + b + temp;</pre>        |  |  |

|                               | 21 | IF (temp > 255) THEN                    |  |  |

|                               | 22 | c8 <= '1';                              |  |  |

|                               | 23 | temp := temp256;                        |  |  |

|                               | 24 | ELSE c8 <= '0';                         |  |  |

|                               | 25 | END IF;                                 |  |  |

|                               | 26 | s <= temp;                              |  |  |

|                               | 27 | END PROCESS;                            |  |  |

| Amin Mehranzadeh, Ph.D.       | 28 | END adder;                              |  |  |

|                               | 29 |                                         |  |  |

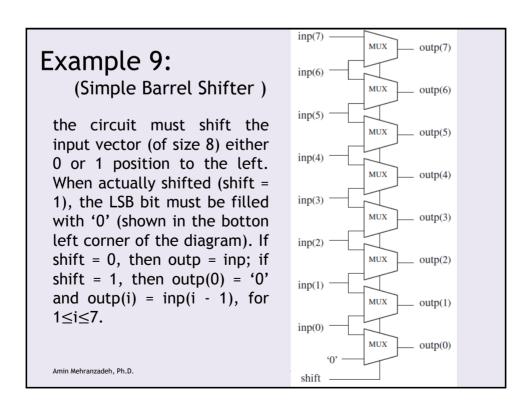

|                                        | 1                                                            |  |  |  |

|----------------------------------------|--------------------------------------------------------------|--|--|--|

| Example 9:<br>(Simple Barrel Shifter ) | 2 LIBRARY ieee;                                              |  |  |  |

|                                        | <pre>3 USE ieee.std_logic_1164.all;</pre>                    |  |  |  |

|                                        | 4                                                            |  |  |  |

|                                        | 5 ENTITY barrel IS                                           |  |  |  |

|                                        | 6 GENERIC (n: INTEGER := 8);                                 |  |  |  |

|                                        | <pre>7 PORT ( inp: IN STD_LOGIC_VECTOR (n-1 DOWNTO 0);</pre> |  |  |  |

|                                        | <pre>8 shift: IN INTEGER RANGE 0 TO 1;</pre>                 |  |  |  |

|                                        | <pre>9 outp: OUT STD_LOGIC_VECTOR (n-1 DOWNTO 0));</pre>     |  |  |  |

|                                        | 10 END barrel;                                               |  |  |  |

|                                        | 11                                                           |  |  |  |

|                                        | 12 ARCHITECTURE RTL OF barrel IS                             |  |  |  |

|                                        | 13 BEGIN                                                     |  |  |  |

|                                        | 14 PROCESS (inp, shift)                                      |  |  |  |

|                                        | 15 BEGIN                                                     |  |  |  |

|                                        | 16 IF (shift=0) THEN                                         |  |  |  |

|                                        | 17 outp <= inp;                                              |  |  |  |

|                                        | 18 ELSE                                                      |  |  |  |

|                                        | 19 outp(0) <= '0';                                           |  |  |  |

|                                        | 20 FOR i IN 1 TO inp'HIGH LOOP                               |  |  |  |

|                                        | <pre>21 outp(i) &lt;= inp(i-1);</pre>                        |  |  |  |

|                                        | 22 END LOOP;                                                 |  |  |  |

|                                        | 23 END IF;                                                   |  |  |  |

|                                        | 24 END PROCESS;                                              |  |  |  |

| Amin Mehranzadeh, Ph.D.                | 25 END RTL;                                                  |  |  |  |

|                                        | 26                                                           |  |  |  |

1 \_\_\_\_\_ Example 10: <sup>2</sup> LIBRARY ieee; 3 USE ieee.std\_logic\_1164.all; 4 \_\_\_\_\_ (Leading Zeros) 5 ENTITY LeadingZeros IS 6 PORT ( data: IN STD\_LOGIC\_VECTOR (7 DOWNTO 0); design below <sup>7</sup>/<sub>8 END LeadingZeros;</sub> zeros: OUT INTEGER RANGE 0 TO 8); The counts the number of 9 END Leadingzeros; leading zeros in a 10 ARCHITECTURE behavior OF LeadingZeros IS binary vector, starting <sup>11 BEGIN</sup> from the left end. In  $\frac{12}{13}$ 12 PROCESS (data) VARIABLE count: INTEGER RANGE 0 TO 8; this example, the loop 14 BEGIN will end as soon as a <sup>15</sup> (1' is found in the data vector. Therefore, it is <sup>16</sup> WHEN FOR i IN data'RANGE LOOP CASE data(i) IS WHEN '0' => count := count + 1; for 19 appropriate WHEN OTHERS => EXIT; counting the number 20 END CASE; of zeros that precedes <sup>21</sup><sub>22</sub> END LOOP; zeros <= count;</pre> the first one. 23 END PROCESS; 24 END behavior; 25 -----Amin Mehranzadeh, Ph.D.